# **European Research Infrastructure supporting Smart Grid Systems Technology Development, Validation and Roll Out**

# Technical Report TA User Project

# Hardware-in-the-Loop Testing of Ancillary Services of Distributed Renewable Energy Sources

Grant Agreement No: 654113

Funding Instrument: Research and Innovation Actions (RIA) – Integrating Activity (IA)

Funded under: INFRAIA-1-2014/2015: Integrating and opening existing national

and regional research infrastructures of European interest

Starting date of project: 01.11.2015

Project Duration: 54 month

Contractual delivery date: 20/01/2020

Actual delivery date: 22/01/2020

Name of lead beneficiary

for this deliverable: José María Maza-Ortega, School of Engineering. University of

Sevilla

Deliverable Type: Report (R)

Security Class: Public (PU)

Revision / Status: Released

Project co-funded by the European Commission within the H2020 Programme (2014-2020)

#### **Document Information**

Document Version: 2.0

Revision / Status: Released

All Authors/Partners Manuel Barragán-Villarejo, José María Maza-Ortega, Fran-

cisco Jesús Matas-Díaz, Milos Cvetkovic and Umer Mush-

taq.

Distribution List ERIGRID Consortium, TU Delft, University of Sevilla

#### **Document History**

| Revision | Content / Changes | Resp. Partner             | Date       |

|----------|-------------------|---------------------------|------------|

| 1        | Final Draft       | Manuel Barragán-Villarejo | 21.01.2020 |

#### **Document Approval**

| Final Approval   | Name            | Resp. Partner | Date       |

|------------------|-----------------|---------------|------------|

| Host Institution | Rishabh Bhandia | TUD           | 21.02.2020 |

#### **Disclaimer**

This document contains material, which is copyrighted by certain ERIGrid consortium parties and may not be reproduced or copied without permission. The information contained in this document is the proprietary confidential information of certain ERIGrid consortium parties and may not be disclosed except in accordance with the consortium agreement.

The commercial use of any information in this document may require a licence from the proprietor of that information.

Neither the ERIGrid consortium as a whole, nor any single party within the ERIGrid consortium warrant that the information contained in this document is capable of use, nor that the use of such information is free from risk. Neither the ERIGrid consortium as a whole, nor any single party within the ERIGrid consortium accepts any liability for loss or damage suffered by any person using the information.

This document does not represent the opinion of the European Community, and the European Community is not responsible for any use that might be made of its content.

#### **Copyright Notice**

© The ERIGrid Consortium, 2015 – 2020

### **Table of contents**

| E | xecı                     | utive Summaryutive Summary                   | 5  |

|---|--------------------------|----------------------------------------------|----|

| 1 | C                        | General Information of the User Project      | 6  |

| 2 | F                        | Research Motivation                          | 8  |

|   | 2.1<br>2.2               |                                              |    |

| 3 | S                        | State-of-the-Art                             | 10 |

| 4 | Е                        | Executed Tests and Experiments               | 12 |

|   | 4.1<br>4.2<br>4.3<br>4.4 | Standards, Procedures, and Methodology       | 16 |

| 5 | F                        | Results and Conclusions                      | 28 |

|   | 5.1<br>5.2<br>5.3        | 2 Integration test of the experimental setup | 36 |

| 6 |                          | Dissemination Planning                       | 48 |

| 7 | F                        | References                                   | 49 |

| 8 | A                        | Annex                                        | 50 |

|   | 8.1                      | List of Figures                              | 50 |

#### **Abbreviations**

AS Ancillary Services

CCS Code Compose Studio

DRES Distributed Renewable Energy Resource

FESS Fast Energy Storage System

HFPS High Frequency Power Smoothing

MPP Maximum Power Point

PHIL Power Hardware-in-the-Loop

PV Photovoltaic SC Supercapacitor

SG Synchronous Generation

TA Trans-national Access

UC Ultracapacitor

VI Virtual Inertia

WP Wind power

WTG Wind Turbine Generation

## **Executive Summary**

The traditional electrical power system has been designed to operate with central, dispatchable conventional power plants with synchronous generation (SG). These SG along with other control assets (transformer tap changers, capacitors, reactors, phase shifting transformers, etc.) provide the required Ancillary Services (AS) for stability and security of power grid. However, with the irruption of massive distributed renewable energy sources (DRESs), displacing the traditional SG, this situation is no longer valid being necessary the contribution of DRES to support the grid stability and security. As a matter of fact, it is expected that this technological change increases the relative AS costs from 5% in 2015 to 25% in 2020 [1]. This fact may represent an excellent opportunity for DRES owners which may consider to invest on new technologies enabling their participation in future AS markets. In spite of many AS are proposed in the specialized literature, this proposal focuses exclusively on the provision of Virtual Inertia (VI) and High-Frequency Power Smoothing (HFPS) which are directly related to the minimization of grid frequency variations. On the one hand, VI tries to emulate the behaviour of traditional SG just after a frequency excursion. On the other hand, HFPS tries to smooth the output power of the DRES due to the uncontrollable nature of the energy resource to mitigate frequency variations. For doing so, it is necessary to effectively control the injected active power to the grid being necessary to incorporate energy storage in the traditional DRES interfaces. Therefore, the objective of this proposal is to test in a Power Hardware-in-the-Loop (PHIL) environment a new DRES interface incorporating in its DC bus the required Fast Energy Storage System (FESS) for providing VI and HFPS. To achieve this objective, several devices are used which to be experimentally have validated operating individually and jointly. Therefore, a series of tests will be designed to achieve the final objective in a safe and robust way.

# 1 General Information of the User Project

| Host research infrastructures | TU Delft                       |

|-------------------------------|--------------------------------|

| Starting date for the access  | November 17 <sup>th</sup> 2019 |

| Acces duration (in weeks)     | 5 weeks                        |

Specifically, the access period of Francisco Jesús Matas-Díaz was from November 17 <sup>th</sup> to December 19 <sup>th</sup> and the access period of Manuel Barragán-Villarejo was from November 17<sup>th</sup> to November 24<sup>th</sup>.

| USER PROJECT PROPOSAL           |                                                                                                     |  |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|

| User Project acronym            | HILT AS-DRES                                                                                        |  |  |  |

| User Project title              | Hardware-in-the-Loop Testing of Ancillary Services of Distributed Renewable Energy Sources          |  |  |  |

| Main scientific/technical field | Control of distributed energy resources                                                             |  |  |  |

| Keywords (5 max., free text)    | Ancillary services, renewable energies, supercapacitor, Voltage source converters, DC/DC converters |  |  |  |

| LEADER OF THE PROPOSING USER GROUP  |                                              |  |  |

|-------------------------------------|----------------------------------------------|--|--|

| Name                                | José María Maza-Ortega                       |  |  |

| Phone                               | +34954481280                                 |  |  |

| E-mail address                      | jmmaza@us.es                                 |  |  |

| Nationality                         | Spanish                                      |  |  |

| Gender Male                         |                                              |  |  |

| Age                                 | 47                                           |  |  |

| Organization name                   | School of Engineering. University of Sevilla |  |  |

| Organization address                | Camino de los Descubrimientos s/n            |  |  |

| Organization website                | <u>www.etsi.us.es</u>                        |  |  |

| Position in organization            | Associate Professor                          |  |  |

| Activity type and legal             | Higher Education Institution                 |  |  |

| status of organization <sup>1</sup> |                                              |  |  |

| MEMBERS OF THE PROPOSING USER GROUP (repeat for all Users) |                                              |  |  |

|------------------------------------------------------------|----------------------------------------------|--|--|

| Name                                                       | Juan Manuel Mauricio                         |  |  |

| Phone                                                      | +34661102056                                 |  |  |

| E-mail address                                             | jmmauricio@us.es                             |  |  |

| Nationality                                                | Italian                                      |  |  |

| Gender                                                     | Male                                         |  |  |

| Age                                                        | 42                                           |  |  |

| Organization name                                          | School of Engineering. University of Sevilla |  |  |

| Organization address                                       | Camino de los Descubrimientos s/n            |  |  |

| Organization website                                       | <u>www.etsi.us.es</u>                        |  |  |

| Position in organization                                   | Associate Professor                          |  |  |

| Activity type and legal                                    | Higher Education Institution                 |  |  |

| status of organization <sup>1</sup>                        |                                              |  |  |

| MEMBERS OF THE PROPOSING USER GROUP (repeat for all Users) |                      |  |  |

|------------------------------------------------------------|----------------------|--|--|

| Name Manuel Barragán-Villarejo                             |                      |  |  |

| Phone +34954481281                                         |                      |  |  |

| E-mail address                                             | manuelbarragan@us.es |  |  |

| Nationality                                                | Spanish              |  |  |

| Gender                              | Male                                         |

|-------------------------------------|----------------------------------------------|

| Age                                 | 35                                           |

| Organization name                   | School of Engineering. University of Sevilla |

| Organization address                | Camino de los Descubrimientos s/n            |

| Organization website                | www.etsi.us.es                               |

| Position in organization            | Assistant Professor                          |

| Activity type and legal             | Higher Education Institution                 |

| status of organization <sup>1</sup> |                                              |

| MEMBERS OF THE PROF                 | POSING USER GROUP (repeat for all Users)     |  |

|-------------------------------------|----------------------------------------------|--|

| Name                                | Francisco de Paula García-López              |  |

| Phone                               | +34954485987                                 |  |

| E-mail address                      | fdpgarcia@us.es                              |  |

| Nationality                         | Spanish                                      |  |

| Gender                              | Male                                         |  |

| Age                                 | 34                                           |  |

| Organization name                   | School of Engineering. University of Sevilla |  |

| Organization address                | Camino de los Descubrimientos s/n            |  |

| Organization website                | <u>www.etsi.us.es</u>                        |  |

| Position in organization            | Researcher                                   |  |

| Activity type and legal             | Higher Education Institution                 |  |

| status of organization <sup>1</sup> |                                              |  |

| MEMBERS OF THE PROPOSING USER GROUP (repeat for all Users) |                                              |  |  |

|------------------------------------------------------------|----------------------------------------------|--|--|

| Name                                                       | Francisco Jesús Matas-Díaz                   |  |  |

| Phone                                                      | +34954485987                                 |  |  |

| E-mail address                                             | fmatas@us.es                                 |  |  |

| Nationality                                                | Spanish                                      |  |  |

| Gender                                                     | Male                                         |  |  |

| Age                                                        | 24                                           |  |  |

| Organization name                                          | School of Engineering. University of Sevilla |  |  |

| Organization address                                       | Camino de los Descubrimientos s/n            |  |  |

| Organization website                                       | <u>www.etsi.us.es</u>                        |  |  |

| Position in organization                                   | Researcher                                   |  |  |

| Activity type and legal                                    | Higher Education Institution                 |  |  |

| status of organization <sup>1</sup>                        |                                              |  |  |

#### 2 Research Motivation

The massive penetration of distributed renewable energy sources (DRES) in the electrical system will bring a series of benefits such as the decarbonisation of electric power generation, energy inde-pendence of countries, a low impact on the environment compared to fossils energy sources and increased of the system efficiency owing to generation and consumption will be in nearby points of the network. However, the replacement of the generation based on fossil origin fuels by the genera-tion of renewable origin not only imply a change of the primary energy source but also of the electrical generation devices and their control which will signify a challenge to operate the electrical system in a stable and efficient way with this new resources.

The traditional electrical power system has been designed to operate with central, dispatchable conventional power plants with synchronous generation (SG). These SGs along with other control assets (transformer tap changers, capacitors, reactors, phase shifting transformers, etc.) provide the required Ancillary Services (AS) for stability and security of power grid. Concretely, the SGs are able to provide almost inherantly inertia and a dispatchable power to the system. However, DRESs replace the SGs by electronic-based generation which by itself is not able to provide inertia to the system and the intermittency of renewable generation leads to the impossibility of generating a dispatchable power. This causes two major problems among others. First, a significant decrease in rotational inertia of the power system which may causes large frequency variations in case severe disturbances leading to frequency instability and blackouts due to operation of islanding relays. Second, the undispatchable nature of the primary energy source (PV or WP) produces continuous variations of the injected power to the system which not only may cause frequency fluctuations but also other problems like voltage flicker. In order to overcome these two shortcomings, the motivation of this work is to explore the provision of two ancillary services (virtual inertial(VI) and high frequency power smoothing (HFPS)) by advanced DRES interfaces incorporating a fast energy storage system (FESS) into the DRES.

#### 2.1 Objectives

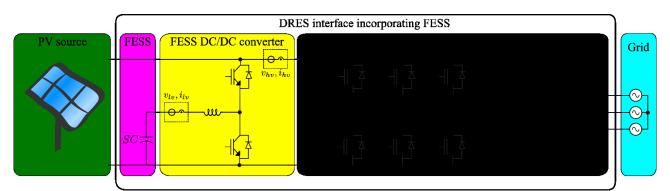

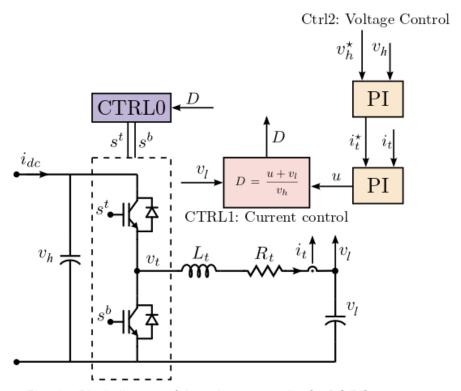

The objective of the project is to test in a power hardware in the loop (PHIL) laboratory the proposed VI and PHFS ancillary services of a DRES interface incorporating a FESS based on a supercapacitor controlled by a DC/DC converter according to the scheme shown in Fig. 1.

Fig. 1. DRES interface incorporating FESS for providing ASs.

The specific objectives of the proposal can be summarized in the following points:

• Experimental validation of the capabilities of the DRES interface for providing VI and PHFS. The design of the power electronic based hardware and the control algorithms requires an experimental validation as a previous step of a real deployment in the distribution system within a pilot project. In this sense, the use of PHIL platforms, where the behaviour of the distribution network can be faithfully reproduced, may prevent design failures or a not-expected behaviour which can be solved in an early design stage.

- Analysis of the deviations with respect to the simulation results. Any deviation with respect to the simulation results has to be carefully analysed. These deviation can be caused by several reasons: (i) the model used in the simulations does not properly represents the actual device; (ii) the designed control algorithm has to be adjusted to consider some aspects that usually are not considered in the initial simulations, e.g. communication delays; (iii) practical issues aspects in power electronic based hardware prototypes dealing with EMC, earthing conditions, etc. which may affect the performance of the device.

- Limitations of the proposed DRES interface. Only with an experimental validation it is possible to assess a technology. The analysis of deviations with respect to simulations will help to identify improvements on the hardware and the control algorithms as well as define those key parameters affecting the final performance of the device.

- Validation of the quantification methodology used for measuring the provided ASs. It is expected that the VI and HPFS functionalities will be incorporated as ASs in the new DRES interfaces. Therefore, new business opportunities from new incomes due to this AS provision are expected. For this reason, it is required to define a metric to measure the contribution of any DRES interface as a previous step of defining its related economic price.

- Definition of a standardized testing methodology. This is a key issue for comparison purposes of different technologies able to provide the envisioned VI and HPFS functionalities.

The testing methodology has to define as clear as possible: (i) testing scenarios for validating VI and HFPS in a separate manner; (ii) quantification metric of the ancillary service; (iii) acceptance criteria used to assess that a given technology provides the VI of HFPS ASs.

#### 2.2 Scope

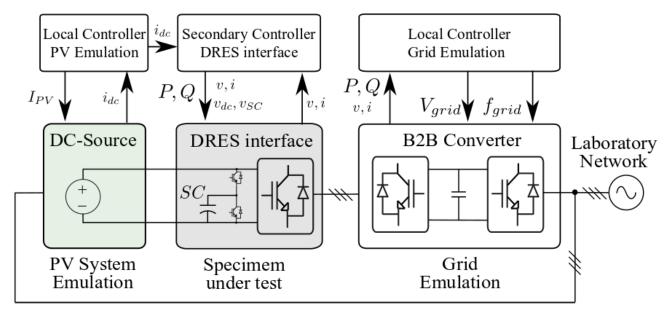

In order to achieve the objectives set out in the previous subsection, it is necessary to have three devices that are capable of reproducing the integration of a DRES into an electric power system. The joint operation of these devices and their control is known as PHIL. The electrical connection of the experimental assembly and the signals exchanged between them is shown in Fig. 2.

Fig. 2. Test setup involving the DRES interface and the PHIL platform.

A brief description of each component is described as follows:

PV System Emulation. The primary energy source is emulated by a controlled DC source.

This source is provided by TU Delft and it allows local control or remote control by externally providing setpoints. Among other functions, this device can reproduce the 24-hour power

profile injected by a plant PV. The energy delivers by the DC source is extracted from the low voltage laboratory network in Delft. The DC source in directly connected to the DC bus of the specimen under test. The current injected by the DC source is sent to the secondary controller of the specimen under test.

- Specimen under test. This device consists of a voltage source converter (VSC) capable of transforming the DC current provided by the PV plant in AC current in order to integrate the PV plant into the electrical system. This is provided by the Universidad de Sevilla and it contains all the coupling filters, measurement, communication and control equipments necessary to perform an efficient DC/AC conversion. In addition, a DC/DC conversion is added into this setup to integrate a SC into the DC bus of the VSC. As a novelty in this configuration, the VSC and DC/DC converter are integrated into a single 4-branch power converter. Three of these branches are used for DC/AC conversion and the fourth branch for DC/DC conversion. This has allowed having a very compact specimen under test and the possibility of using a single control and communication board to operate both converters. The VI and HFPS functionalities are incorporated into this device. In order to adequately provide both functionalities, the control system requires the current injected by the DC source.

- Grid Emulation. The behavior of the electrical system will be reproduced by a back-to-back (B2B) converter provided by TU Delft. This consists of an AC/DC /AC converter where it primary side is feed from the laboratories' low voltage network (with a fixed frequency and voltage) converting the AC current into DC current to convert back to AC current in a secondary side with a desired amplitude and frequency. In this way, the secondary side is able to reproduce any disturbance, whether voltage or frequency, in an electrical system. This side is connected directly to the AC side of the specimen under test.

The three devices are based on power electronics converters with different characteristics: conversion levels, connection filters, switching frequencies, resonance frequencies, switching techniques, control strategies, etc... Therefore, the joint connection of these equipment is complex because the iteration between them can damage them. A series of tests, which will be described in section 4, have been designed to validate the correct operation of each equipment individually. Next, the operation of the devices is validated in pairs and, finally, the full experimental assembly with the three equipments is tested to fulfill the proposed objectives.

#### 3 State-of-the-Art

As previously stated, the constant replacement of conventional SG with electronic-based generation resources such as photovoltaic (PV), wind power (WP) plants causes two major problems among others. First, a significant decrease in rotational inertia of the power system which may causes large frequency variations in case severe disturbances leading to frequency instability and blackouts due to operation of islanding relays. Second, the undispatchable nature of the primary energy source (PV or WP) produces continuous variations of the injected power to the system which not only may cause frequency fluctuations but also other problems like voltage flicker. In order to overcome these two shortcomings, this proposal explores the provision of two ancillary service by advanced DRES interfaces incorporating a FESS:

Virtual Inertia (VI). Recently, numerous methodologies have been proposed [2],[3],[3] in order to make DRES, particularly Wind Turbine Generator (WTG) exhibit virtual inertia. In fact, some of them have already been implemented in commercially available WTG [5]. These methodologies mainly focus on altering the rotational speed of the WTG to provide an inertial response. However, this approach provides an inertial response that depends on the operating point of the WTG and causes additional stress on the mechanical parts of the WTG [6]. In the case of DRES without rotating masses (e.g. PV), it has been suggested to operate them below their Maximum Power Point (MPP), so that some additional active power can be provided in under-frequency events [7]. Although this approach is effective due to the ability of PV control systems to move very fast from one operating point to another, it forces the DRES to operate continuously (or for very long periods) with curtailed

- power, decreasing the respective revenues. The proposed approach envisions enabling all DRES to provide controllable inertia by adding a FESS (a super-capacitor bank) controlled by a dedicated DC/DC converter. This solution will report benefits to both WTG and PV because a reduction of the mechanical stress and operation without curtailment can be obtained respectively.

- High Frequency Power Smoothing (HFPS). Power smoothing is becoming a significant issue in case of large DRES penetration in weak power grids. For this reason, grid operators limits the active power ramps (ΔP/Δt) in the grid codes which determines the minimum technical requirements of connection [2],[8]. This problem is usually faced by two possible strategies. In the first category, short-term storage systems, such as super-capacitors [9], batteries [10], flywheels, superconducting energy storage, and fuel cells are used for minimizing the effect of power fluctuations [11]. The second category includes advanced control algorithms trying to minimize the output power variations. In case of WPG the kinetic energy of the inertia control [12] and the pitch angle control [13], can be used for power smoothing. However, the mitigation of the power fluctuation is achieved on a range of power variations depending on the rather slow time constants of the mechanical/hydraulical controllers. In addition, and unfortunately, this control strategies are no longer valid in case of PV generation.

However, and in spite of these contributions, to the knowledge of the members of this user group some gaps can be found in the state of the art. On the one hand, it has to be considered that the business model associated to these ASs has to be carefully analysed to check their profitability. For doing so, it is required to estimate the AS cost. Therefore, it is necessary to develop a **metric to properly quantify the provided AS** and, after that, to transform this technical parameter into an economic cost. On the other hand, there are no **standardized testing protocols to check the capability of providing ASs** of these new DRES interfaces. The proposal will elaborate on this to facilitate the deployment of this technology.

#### 4 Executed Tests and Experiments

As mentioned above, a series of tests will be carried out individually, in pairs and grouping the whole set so that in a robust and safe way we are able to connect the three power electronics devices and achieve the proposed objectives. The following describes the unitary tests carried out on each device, the progressive integration between the different devices until all of them are fully integrated to provide the auxiliary services of inertia and HFPS.

#### 4.1 Test Plan

#### 4.1.1 Unitary Tests

The devices provided by TU Delft are commercial equipment that guarantees its correct operation safely. Therefore, the individual tests performed on these devices are ignored in this document because they were only performed to verify their proper functioning. Individual tests performed on the specimen under test and provided by USE are detailed below. This is the fundamental device since it contains the control strategies developed by the research team to provide the ASs. Voltages and currents generated by the DRES interface are recorded using an oscilloscope provided by TU Delft.

#### 1. Open Loop of the AC/DC converter

AC/DC converter is connected to a three-phase resistive load defining perfect sinusoidal signals for the modulation of the voltage source converter. The DC voltage of the VSC must be controlled by an external DC voltage source (0-730 Vdc).

# 2. AC/DC converter working in Grid-Feeding mode and connected to grid through a transformer

The AC/DC converter works as a STATCOM controlling the DC voltage of its DC bus and "reactive current (*id*)". The low voltage side of the transformer is connected to the AC side of AC/DC converter and the high voltage side is connected to the LV grid of the laboratory in Delft.

#### 3. AC/DC converter working in Grid-Feeding mode and connected directly to grid

The AC/DC converter works as a STATCOM controlling the DC voltage of its DC bus and "reactive current (*id*)". The AC/DC converter is connected to the LV grid of the laboratory in Delft.

#### 4. Open Loop of the DC/DC converter

The DC/DC converter is connected to a resistive load defining a constant signal for the modulation of the converter. The resistor is connected to the low voltage side of the DC/DC converter and an external DC voltage source (0-730 Vdc) must control the high voltage side of the converter.

# 5. Current controller of the DC/DC converter with resistor

The current control loop of the DC/DC converter is tested controlling the current circulating by a resistive load. The resistor is connected to the low voltage side of the DC/DC converter and an external DC voltage source (0-730 Vdc) must control the high voltage side of the converter.

### 6. Current controller of the DC/DC converter with supercapacitor

The current control loop of the DC/DC converter is tested charging and discharging the SC. The SC is connected to the low voltage side of the DC/DC converter and an external DC voltage source (0-730 Vdc) must control the high voltage side of the converter

# 7. Voltage controller of the DC/DC converter with supercapacitor and DC bus of the AC/DC converter

The voltage control loop of the DC/DC converter is tested to control the voltage of the DC bus in the AC/DC converter. The SC is connected to the low voltage side of the DC/DC converter and a DC bus of the AC/DC converter is connected in the high voltage side of the DC/DC converter.

#### 8. Open Loop AC/DC converter. Voltage Controller DC/DC converter

AC/DC converter is connected to a three-phase resistive load defining perfect sinusoidal signals for the modulation of the voltage source converter. The voltage control loop of the DC/DC converter controls the voltage of the DC bus in the AC/DC converter.

# 9. Grid-Feeding connected to grid through a transformer AC/DC converter. Voltage Controller DC/DC converter.

The voltage control loop of the DC/DC converter controls the voltage of the DC bus in the AC/DC converter. The low voltage side of the transformer is connected to the AC/DC converter and the high voltage side is connected to the LV grid of the laboratory in Delft. The current control loop (currents *id* and *iq*) of the AC/DC converter is tested.

#### 10. Grid-Feeding connected to grid AC/DC converter. Voltage Controller DC/DC converter.

The voltage control loop of the DC/DC converter controls the voltage of the DC bus in the AC/DC converter. The AC/DC converter is connected to the LV grid of the laboratory in Delft. The current control loop (currents *id* and *iq*) of the AC/DC converter is tested.

#### 4.1.2 Integration test of the experimental setup

The following describes the tests performed when two or more devices are involved in the experimental setup. The objective of these integration tests is to gradually incorporate the joint operation of the equipment involved in the final experimental setup.

#### Integration of Grid Emulation and DC/AC converter of DRES interface

This test consists of connecting Grid Emulation to DRES interface.

- Objective: AC/DC converter is controlled as a STATCOM (Control of the DC voltage and AC current *id*) and grid emulator generates a three phase balanced 50 Hz AC-voltage.

- Electrical installations: A contactor is used to connect and disconnect both devices.

- Previous tests before connecting both devices: The output of Grid Emulation is connected to the input of the contactor. The output of the contactor is connected to resistors. A three phase balanced 50 Hz AC-voltage is generated by Grid Emulation. The interconnection filter selected for grid emulator is a LC-filter. The initial voltage is set to 50 Volts rms phase-neutral and its value is increased progressively. The maximum current delivered by Grid Emulation is set equal to 5 A. If voltages are properly generated, the contactor provided by TUDelft can be closed to feed the resistors. After closing the contactor, recording the voltages measured by the oscilloscope and monitoring the voltages measured by the DSP and CCS. Check that the measurements of the oscilloscope and the CCS are similar (rms, sequence, frequency, waveform etc ...). Voltages and currents are recorded through an oscilloscope provided by TU Delft and their harmonic spectrum is analyzed to review the proper operation of the grid emulator. Especially be attentive to low order harmonics and switching ones of the grid emulation (it is assumed to be 16 kHz).

• A simulation using Matlab Simulink is made emulating both devices to faithfully reproduce the behavior of grid emulator and DRES interface in a simulation environment.

#### 2. Integration of PV emulator and DC/AC converter of the DRES interface

This test consists in connecting PV emulator as a current source to DRES interface working as a STATCOM.

- Objective: DC/AC converter of the DRES interface is connected to the low voltage laboratory network controlling reactive power injected and the DC link voltage. Active power injected to the grid is provided by PV emulator which is connected to the DC bus of the DC/AC converter.

- Electrical installations: A contactor among DRES interface and the low voltage laboratory network is installed to connect o disconnect the device from the grid. Moreover, a breaker is connected among PV emulator and the DC bus to connect and disconnect it from the DC/AC converter.

- Previous tests: Resistors are connected to the output of PV emulator which works as a current source. The current supplied to the resistors is increased progressively. The objective is to check the PV emulator behavior when the voltage at its terminal is higher than a maximum voltage limit defined for protection. At that moment, the control mode of PV emulator should change from current control mode to voltage current mode to avoid overvoltages in the system.

# 3. Integration of PV emulator, DC/AC converter of DRES interface and Grid Emulation

This test consists in connecting PV emulator as a current source to the DC bus of the DC/AC converter into the DRES interface which operates as a STATCOM. In addition, the AC side of the prototype is connected to the Grid Emulator which replaces the low voltage laboratory network with respect to the previous test.

- Objective: Grid Emulator is in charge to generate a controlled three-phase balanced 50 Hz voltage. The AC side of the DC/AC converter is connected to the Grid Emulator in order to control the reactive power injected into the Grid Emulator and the DC link voltage of its DC bus. PV emulator is connected to the DC bus of the DC/AC converter injecting active power which is evacuated to the Grid Emulator by the DC/AC converter.

- Electrical installations: A contactor among DRES interface and Grid Emulator is connected.

In addition, a transformer Yd5 is connected among Grid Emulator and DRES interface. Finally, a breaker must be connected among PV emulator and the DC bus of the DC/AC converter.

- Previous tests: No previous tests are necessary.

# 4. Integration test of Grid Emulation, DC/AC converter and DC/DC converter of DRES interface

This test consists of connecting Grid Emulator to the full-operating DRES interface. Ultracapacitor will be in charge of controlling the DC link Voltage and the AC-DC converter will work to control the current *id* and *iq*. In addition, a new controller will be in charge of maintaining the voltage of the ultracapacitor within the technical limits.

Objective: Grid Emulator will generate a controlled three-phase voltage. EASY-RES Prototype will be connected to the Grid Emulator, with AC-DC and DC-DC operative, controlling reactive power injected and the DC link voltage.

- Electrical installations: A contactor among AC-DC converter and Grid Emulator must be installed. Moreover, a transformer Yd5 is connected among Grid Emulator and DC/AC converter.

- Previous tests: The ultracapacitor must be charged to a safe value in order to have enough capacity to charge and discharge it.

# 5. Integration test of PV emulator, DC/AC converter and DC/DC converter of DRES interface

This test consists of connecting PV emulator as a current source to the DRES interface. The DC bus will be controlled by the DC/DC converter and the AC/DC will inject active and reactive power to the low voltage laboratory network.

- Objective: The AC/DC converter is connected to the low voltage laboratory network and the ultracapacitor to the DC bus of the AC/DC converter through DC/DC converter. The AC/DC converter controls the active and reactive power injected to the grid and the DC/DC converter the voltage level of the DC bus. In addition, the PV emulator is connected to the DC bus of the AC/DC converter. In this way, the active power injected by PV emulator must be evacuated by the AC/DC converter to avoid overloaded the ultracapacitor.

- Electrical installations: A contactor among AC-DC converter and Grid Emulator must be installed. Moreover, a transformer Yd5 is connected among low voltage grid and DC/AC converter. Finally, a breaker must be connected among PV emulator and the DC bus.

- Previous tests: The ultracapacitor is charged until 120 V.

## 4.1.3 Provision of auxiliary services corresponding to Inertia and HFPS

The previous tests have served to verify the correct operation and the control implemented of each of the equipment used in the assembly in an individual and joint way. Once its correct operation has been verified, it is ready to propose the tests that allow us to validate if the DRES interface is able to provide the auxiliary services of inertia and HFPS.

#### 1. Active power injected from the UC emulating a specific inertia and HFPS request

PV emulator acts like a current source injecting active power into the DC bus of the DC/AC converter. This power is evacuated by the DC/AC converter of the DRES interface into the grid emulator which generates a three-phase balanced voltage. The UC is connected to the DC bus of the DC/AC converter thorugh the DC/DC converter which is in charge to control the DC voltage of the DC bus.

- Objective: If the power injected by the PV emulator is evacuated by the DC / AC converter, the system is in steady-state. If there is any difference between both powers, the ultracapaci-tor will take care of this difference to fulfill the power balance. However, the UC may assume this mission for a limited time since its energy is limited. This is the specific case of provision of inertia and HFPS through the DRES interface where a power is required to the UC during a certain time, thus differing the power of the DC / AC converter with respect to the PV emu-lator. The objective of this test is to progressively subject to different imbalances between the power of the AC / DC converter and the PV emulator to find the operating limits of the UC. That is, how much power and for how long the UC can deliver power respecting its technical operating limits.

- Electrical installations: A contactor is installed among DRES interface and grid emulator.

Moreover, a breaker must be connected among PV emulator and the DC bus of the DC/AC converter.

- Previous tests: The ultracapacitor must be charged until a specific value.

#### 4.2 Standards, Procedures, and Methodology

This section defines the operation protocol of subsection 4.1.2 and 4.1.3 which involves two or more devices in the experiment setup. These operation protocols must be made in a safe way to validate each control strategy which will be defined in the next subsection for each device. The operation protocol of each test is defined below:

### 1. Integration of Grid Emulation and DC/AC converter of DRES interface

Operation protocol to operate both devices:

- 1. Maximum current and maximum DC voltage allowed in DRES interface is set equal to 10 A and 200 V respectively. This is defined in the controller of the DRES interface

- 2. A three phase balanced 50 Hz and 50 Volts rms phase-neutral AC-voltage is generated by Grid Emulation. The maximum current allowed in Grid Emulation is set equal to 10 A.

- 3. Contactor provided by TUDelft is closed.

- 4. Voltages generated by Grid Emulator are checked in code composer studio (CCS) (rms, sequence, frequency etc..). This is the local software controller of the DRES interface.

- 5. Precharge of the DC bus of the DRES interface. For this purpose, an internal contactor of the DRES interface named Kp is operated until the DC voltage achieves a value of 100V.

- 6. At that moment, Kp is opened and contactor Kg is closed which connects directly the DRES interface to the Grid Emulation. DC Voltage value should be around 122 V in the DC bus.

- 7. All measurements are reviewed in CCS.

- 8. A setpoint of 175 V for the DC voltage and 0 Amps for *id* are consigned to the DRES interface

- 9. At that moment, control signals are sent from the CCS to the DRES interface to track the references. Oscilloscope monitors the currents injected by the DRES interface. Specially, the transient interconnection must be registered by the oscilloscope. If a fault appears in CCS by overcurrents, two actions can be made:

- Increase the overcurrent limits. For this voltage level, the maximum value should be

15 A in Grid Emulation and DRES interface.

- Setpoint of DC-Voltage is reduced to 150-160 V and then increasing to 175V.

- 10. If DRES interface is not connected to Grid Emulation with the previous actions, a transformer could be added between both devices.

- 11. If DRES interface is connected to Grid Emulation, current *id* must be progressively injected. Maximum 5 A. Register the steady state currents in the oscilloscope.

- 12. Analyze the harmonic spectrum of the currents injected into the network. These should contain fundamental frequency for low order harmonics and 10 kHz for switching frequencies.

This test should be repeated to 100V, 150 V and 230 V in Grid Emulator. The maximum value defined and setpoint of each voltage are collected in this table:

| Grid       | Grid     | DC/AC     | DC/AC     | DC/AC     | DC/AC     | DC/AC             |

|------------|----------|-----------|-----------|-----------|-----------|-------------------|

| Emulator   | Emulator | converter | converter | converter | converter | converter         |

| AC Voltage | AC       | Maximum   | Maximum   | DC-       | DC-       | Maximum <i>Id</i> |

| Phase-     | Maximum  | DC        | current   | voltage   | voltage   | setpoint          |

| Neutral    | current  | voltage   | (peak)    | precharge | setpoint  |                   |

|            | (peak)   |           |           |           |           |                   |

| 100 V      | 15 A     | 400 V     | 15 A      | 210 V     | 350 V     | 10 A              |

| 150 V      | 20 A     | 600 V     | 20 A      | 320 V     | 525 V     | 15 A              |

| 230 V      | 25 A     | 800 V     | 25 A      | 500 V     | 730 V     | 20 A              |

#### 2. Integration of PV emulator and DC/AC converter of the DRES interface

The protocol of this test is defined as follows:

- 1. A Resistor of 60  $\Omega$  is connected to the output of PV emulator.

- 2. PV emulator must be configured as a current source.

- 3. The limits of PV emulator are set in 5 A maximum and 120 V maximum.

- 4. Increase the current toward the resistors until 2A achieving the maximum allowed voltage.

- 5. Check if the operation mode of PV emulator automatically changes from current mode to voltage mode or if it disconnects.

- Simulation: A simulation is made emulating both devices. At first, PV emulator is emulated as an ideal current source. However, a second simulation must be made considering all the power electronics and filters of the PV emulator.

- Operation protocol to operate both devices:

- 1. The limits of PV emulator are set to 750 V and 6 A.

- 2. The DRES interface is connected to the low voltage laboratory network according to the steps 5-9 defined in the previous test.

- 3. When DC link is controlled, and *id* injected is null, connect PV emulator to the DC bus with 0 A setpoint.

- 4. Then, the current of PV emulator is increased until 1 A. Check in CCS the current *Iq* and the currents monitored on the oscilloscope.

- 5. If the controller tracking is working in a good performance the current of the PV emulator is progressively increased until 5A.

- 6. Finally, a setpoint of current *Id* is defined for the DC/AC converter and the current injection is monitored in CCS and oscilloscope.

#### 3. Integration of PV emulator, DC/AC converter of DRES interface and Grid Emulation

Operation protocol to operate the devices:

- 1. A three-phase balanced 50 Hz and 50 Volts rms phase-neutral AC-voltage is generated by Grid Emulation. A maximum current of 10 A is defined for the Grid Emulator.

- 2. Maximum current in DC/AC converter is set equal to 10 A. Maximum DC voltage equal to 200 V.

- 3. Contactor among Grid Emulator and DRES interface is closed.

- 4. Voltages are checked in CCS (rms, sequence, frequency etc..)

- 5. PV emulator is enabled as a current source with 0 A of setpoint. Technical limits for voltages and currents are defined in 200 V and 5 A respectively.

- 6. Precharge of the DC/AC converter as described in the first test of this section. Close Kp until the DC voltage is 100 V.

- 7. A setpoint of 175 V for the DC voltage and 0 Amps for *id* is defined for the AC/DC converter.

- 8. At that moment, control signals are sent from the CCS to the DRES interface to track the references. Oscilloscope monitors the currents injected by the DRES interface. Specially, the transient interconnection must be registered by the oscilloscope. If a fault appears in CCS by overcurrents, two actions can be made:

- Increase the overcurrent limits. For this voltage level, the maximum value should be

15 A in Grid Emulation and DRES interface.

- Setpoint of DC-Voltage is reduced to 150-160 V and then increasing to 175V.

- 9. If DRES interface is not connected to Grid Emulation with the previous actions, a transformer could be added between both devices.

- 10. If DRES interface is connected to Grid Emulation, a 2 A current is progressively injected from the PV emulator to the DC bus of the DC/AC converter. Check current *Id* and *Iq* in CCS and the currents monitored with the oscilloscope.

- 11. Then, a current *id* must be progressively injected. Maximum 5 A. Register the steady state currents in the oscilloscope.

- 12. Analyze the harmonic spectrum of the currents injected into the network. These should contain fundamental frequency for low order harmonics and 10 kHz for switching frequencies.

This test should be repeated to 100V, 150 V and 230 V in Grid Emulator. The maximum value defined and setpoint of each voltage are collected in this table:

| Grid     | Grid     | DC/AC     | DC/AC     | DC/AC     | DC/AC     | DC/AC     | PV       |

|----------|----------|-----------|-----------|-----------|-----------|-----------|----------|

| Emulator | Emulator | converter | converter | converter | converter | converter | emulator |

| AC       | AC       | Maximum   | Maximum   | DC-       | DC-       | Maximum   | max I    |

| Voltage  | Maximum  | DC        | current   | voltage   | voltage   | ld        |          |

| Phase-   | current  | voltage   | (peak)    | precharge | setpoint  | setpoint  |          |

| Neutral  | (peak)   | _         |           |           |           |           |          |

| 100 V    | 15 A     | 400 V     | 15 A      | 210 V     | 350 V     | 10 A      | 3 A      |

| 150 V    | 20 A     | 600 V     | 20 A      | 320 V     | 525 V     | 15 A      | 5 A      |

| 230 V    | 25 A     | 800 V     | 25 A      | 500 V     | 730 V     | 20 A      | 10 A     |

# 4. Integration test of Grid Emulation, DC/AC converter and DC/DC converter of DRES interface

Operation protocol to operate the devices:

- 1. A three-phase balanced 50 Hz and 50 Volts rms phase-neutral AC-voltage is generated by Grid Emulation. A maximum current of 10 A is defined for the Grid Emulator.

- 2. The initial voltage of the ultracapacitor is set to 30 V.

- 3. Maximum current in DC/AC converter is set equal to 10 A. Maximum DC voltage equal to 200 V.

- 4. Contactor among Grid Emulator and DRES interface is closed.

- 5. Voltages are checked in CCS (rms, sequence, frequency etc..)

- 6. PV emulator is enabled as a current source with 0 A of setpoint. Technical limits for voltages and currents are defined in 200 V and 5 A respectively.

- 7. Precharge of the DC/AC converter as described in the first test of this section. Close Kp until the DC voltage is 100 V.

- 8. A setpoint of 175 V for the DC voltage and 0 Amps for *id* and *iq* is defined for the AC/DC converter.

- 9. The DC/DC converter begins to control the DC voltage of the DC bus into the DC/AC converter.

- 10. When the DC voltage reference is achieved, the DC/AC converter begins to inject the current references id and *iq* defined in step 8.

- 11. Analyze the harmonic spectrum of the currents injected into the network. These should contain fundamental frequency for low order harmonics and 10 kHz for switching frequencies.

This test should be repeated to 100V, 150 V and 230 V in Grid Emulator. The maximum value defined and setpoint of each voltage are collected in this table:

| Grid     | Grid     | DRES      | DRES      | DRES      | DRES      | DRES        | Ucap    |

|----------|----------|-----------|-----------|-----------|-----------|-------------|---------|

| Emulator | Emulator | interface | interface | interface | interface | interface   | initial |

| Voltage  | Maximum  | Maximu    | Maximum   | DC-       | DC-       | Maximum     | voltage |

| Phase-   | current  | m DC      | current   | voltage   | voltage   | Id setpoint |         |

| Neutral  | (peak)   | voltage   | (peak)    | precharg  | setpoint  |             |         |

|          |          |           |           | е         |           |             |         |

| 100 V    | 15 A     | 400 V     | 15 A      | 210 V     | 350 V     | 10 A        | 60 V    |

| 150 V    | 20 A     | 600 V     | 20 A      | 320 V     | 525 V     | 15 A        | 90 V    |

| 230 V    | 25 A     | 800 V     | 25 A      | 500 V     | 730 V     | 20 A        | 120 V   |

# 5. Integration test of PV emulator, DC/AC converter and DC/DC converter of DRES interface

Operation protocol to operate the devices:

- 1. The voltage and current limits of PV emulator are set to 750V and 6A respectively.

- 2. The DC/DC converter begins to control the DC voltage of the DC bus with a setpoint of 730V

- 3. When the DC voltage is controlled, the AC/DC converter is connected to the grid injecting 0 A of current *id* and *iq*.

- 4. Then, the PV emulator is connected injecting 0 A into the DC bus of the AC/DC converter.

- 5. The current injected by PV emulator is increased until 1 A. This current is monitored in CCS and oscilloscope.

- 6. If the current tracking and its waveform presents a good performance, the current injected by PV emulator is increased until 5 A.

- 7. Finally, the current *id* injected by the AC/DC converter is increased progressively. Continuously, the current is checked in CCS and oscilloscope.

# 6. Integration test of Grid Emulation, PV emulator, DC/AC converter and DC/DC converter of DRES interface

Operation protocol to operate the devices:

- 1. Control DC bus voltage at VDC given in the chart

- 2. Grid emulator will operate at AC voltage reference given in the chart

- 3. Connect Cinergia as a current source with 1 A setpoint.

- 4. Set the UC voltage reference to VUC nominal as the given chart

- 5. DC bus limit is Vmin and Vmax are set according to the Chart values.

- 6. Start the current reference form the minimum reference to maximum current reference and maximum pulse time for each test.

- 7. Verify system reference and record the waveform for each test to understand the test setup limits.

## 7. Active power injected from the UC emulating a specific inertia and HFPS request

Operation protocol to operate the devices:

- 8. Control DC bus voltage at VDC given in the chart

- 9. Grid emulator will operate at AC voltage reference given in the chart

- 10. Connect Cinergia as a current source with 1 A setpoint.

- 11. Set the ultra-cap voltage reference to VUC nominal as the given chart

- 12. DC bus limit is Vmin and Vmax are set according to the Chart values.

- 13. Start the power reference form the minimum reference with minimum pulse time and step by step increase it to maximum power reference and maximum pulse time for each test.

- 14. Verify system reference and record the waveform for each test to understand the test setup limits.

#### 4.3 Test Set-up(s)

#### 4.3.1 Equipment and communication involved

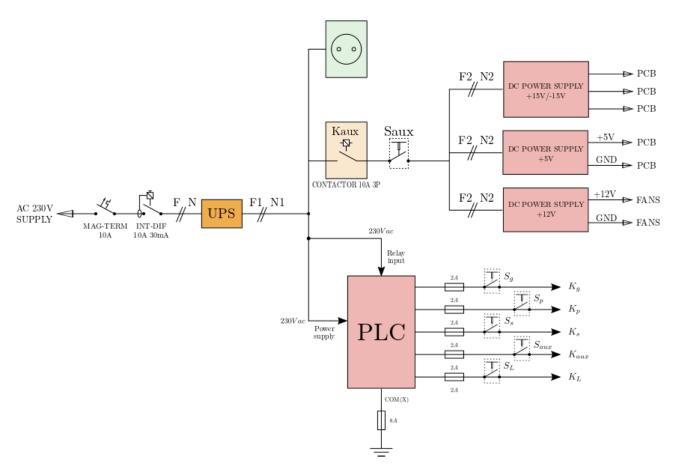

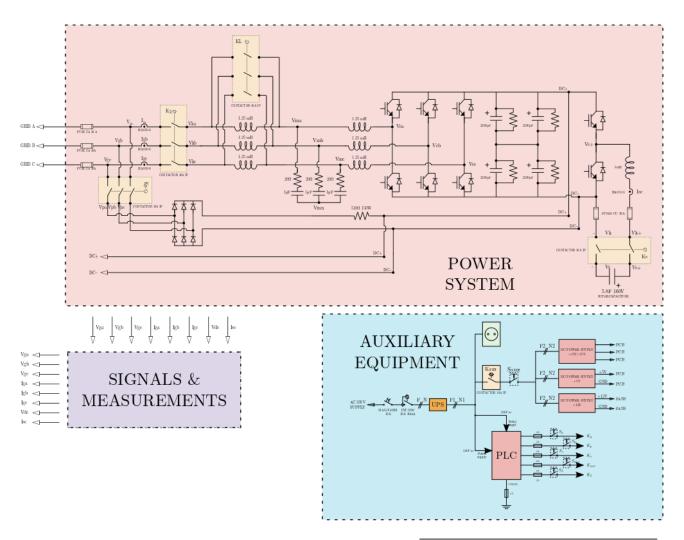

The DRES interface is composed of the following equipments which are depicted in and Fig. 3 and Fig. 4:

- Ultracapacitor of 6 F and 160 V

- DC/DC converter to interconnect the the UC to the DC bus of the DC/AC converter. Rated voltage 800 V and rated current 40 A.

- Inductive filter of DC/DC converter of 3 mH

- DC/AC converter of DC rated voltage equal to 800 V, AC rated voltage of 400 V and rated current of 40 A.

- LCL filter for the AC/DC converter equal to 1.25 mH, 4 μF and 1.25 mH.

- Voltage and currents measurements using LV-25P transducers and HAS-50S tranducer respectively.

- Internal contactors for connect, disconnect and precharge the different power converter of DRES interface

- A digital signal processor (DSP) to register the analog measurements from the transducers, implement the control strategies of the DC/DC and DC/AC converter and send the control signals to the power converters.

- A PCB board which receives the analog measurements from transducers, adapts the signals to the DSP, contains antialiasing filters, the DSP and generate the PWM signal to the power converters.

- Auxiliary devices to operate the DRES interface: power supplies, protection etc..

- A secondary controller to define the setpoints of the power converter and receive some measurements from the power converter. This is connected to the DSP through a CAN communication protocol.

Fig. 3. Auxiliary devices of the DRES interface

| Measurement | Type            | M. Range       | S. Range   |

|-------------|-----------------|----------------|------------|

| $V_{gabc}$  | Sinusoidal      | [-320V, +320V] | [-5V, +5V] |

| $I_{gabc}$  | Sinusoidal      | [-150A, +150A] | [-4V, +4V] |

| $V_{DC}$    | Constant value. | [0V, +1.312kV] | [0V, +5V]  |

| $V_{SC}$    | Constant value. | [0V, +320V]    | [0V, +5V]  |

| $I_{SC}$    | Constant value. | [-150A, +150A] | [-4V, +4V] |

| Parameter  | Value   | Description                 |

|------------|---------|-----------------------------|

| $S_n$      | 20  kVA | Nominal Power.              |

| $f_n$      | 50  Hz  | Nominal Network frequency.  |

| $f_1$      | 20  kHz | Switching frequency.        |

| $V_{gabc}$ | 400 V   | Networt nominal AC voltage. |

| $I_{gabc}$ | 30 A    | Nominal AC current.         |

| $V_{DC}$   | 730 V   | Nominal DC-link voltage.    |

| $P_{SC}$   | 5  kW   | Maximum SC power.           |

| $V_{SC}$   | 160 V   | Nominal SC voltage.         |

| $I_{SC}$   | 30 A    | Nominal SC current.         |

Fig. 4. Electrical and communication scheme of the DRES interface.

A picture of the DRES interface is shown in Fig. 5. The DC/DC and DC/AC converter are unified in a device together with coupling filters, UC, measurements, auxiliary devices and PCB board in order to compact both power converters. This allows to use a single electrical enclosure to assembly the DRES interface.

PV emulator is a commercial device provided by Cinergia. It is composed of an AC/DC and DC/DC converter capable of controlling the current or voltage of the DC/DC converter. An user interface is also used to define the setpoints and the technical limits of Cinergia. This is implemented in a Host PC which is communicated with the power converter via Ethernet standard.

Grid Emulation is a commercial device provide by Triphase. It is composed of two VSCs sharing a common DC bus. This device allows to work as a source of AC current or voltage. Similarly to PV emulator, an user interface is also used to define the setpoints and the technical limits of Cinergia. This is implemented in a Host PC which is communicated with the power converter via Ethernet

#### standard.

Fig. 5. Electrical Enclosure of the DRES interface.

#### 4.3.2 Control strategies

The different tests presented in section 4.1.1 are based on a series of control strategies that are defined and referenced below for each device. Special attention will be given to the control implemented in the DRES interface as they are the strategies designed by the research group.

#### 1. Control strategies for DC/AC converter of DRES interface.

The control strategies of this power converter is made in *dq* coordinates. Specifically, the currents *id* and *iq* injected into the PCC are controlled using the control strategy defined in [16]. From this current control, several operation modes can be implemented in the power converter depending if its dc voltage is controlled by itself or a second device.

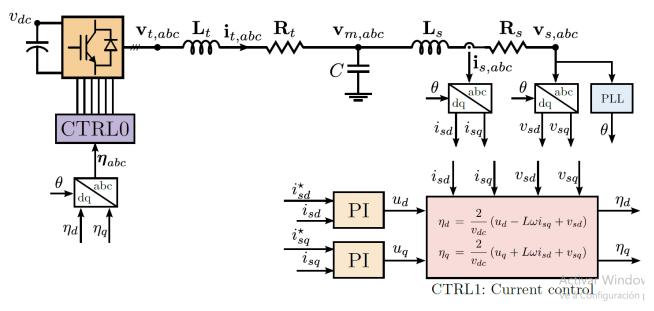

Operation mode: Grid-feeder current control id and ig

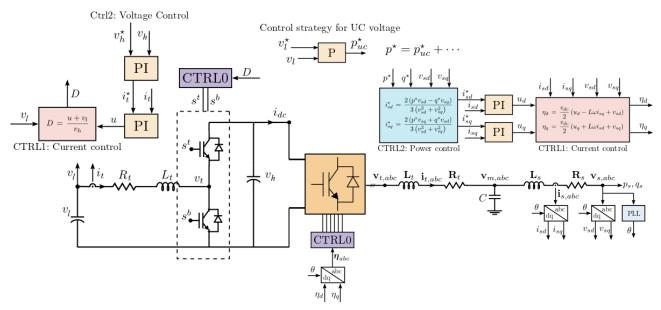

The DC voltage of the DC/AC converter is controlled by a second device. In this way, current *id* and *iq* can be independently controlled by the DC/AC converter. These currents are related with the powers injected into the PCC. Current *id* allows to control the reactive power injected into the PCC and *iq* the active power. The control strategy is depicted in Fig. 6.

Fig. 6. Block diagram of the current controller in dg coordinates for grid-feeder AC/DC converter.

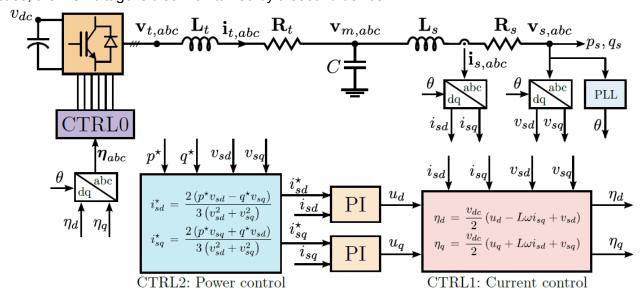

#### • Operation mode: Grid-feeder power control P and Q

As mentioned above, the *id* and *iq* current control allows to control the active and reactive powers injected into the PCC. Fig. 7 shows this control strategy used in this mode of operation. In this case, the DC voltage is also maintained by a second device.

Fig. 7. Block diagram of the power controller in dq coordinates for grid-feeder AC/DC converter.

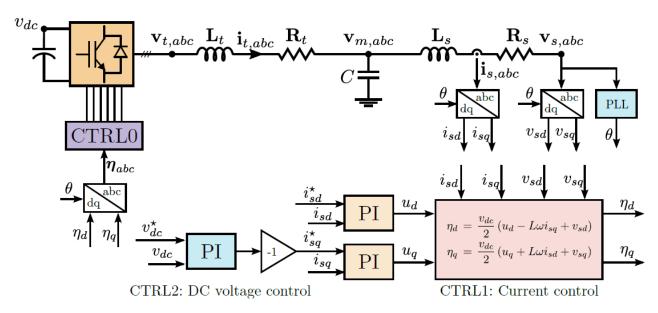

#### Operation mode: Grid-feeder as a STATCOM

In this operation mode, the power controller controls its DC voltage and the current *id* or reactive power injected in the PCC. This control strategy is represented in Fig. 8.

Fig. 8. Block diagram of the DC voltage controller in dq coordinates for grid-feeder STATCOM of DC/AC converter

## 2. Control strategies for DC/DC converter of DRES interface.

Similarly to the controller of the DC/AC converter, the control strategies of this power converter will depends if the DC bus of the DRES interface is controlled by the DC/DC converter or a second device.

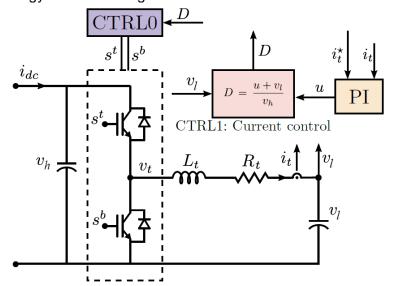

## Operation mode: Current control of the DC/DC converter

The DC voltage of the DC bus in the DRES interface is controlled by a second device. This corresponds to the high voltage side of the DC/DC converter. The low voltage side of the DC/DC contains the UC together its coupling inductive filter. In this way, a current controller can be implemented to charge and discharge the UC controlling the current circulating through the inductive filter. This control strategy is shown in Fig. 9.

Fig. 9. Block diagram of the current controller for DC/DC converters.

#### Operation mode: Voltage control of the DC/DC converter

The DC/DC converter is in charge to control the DC voltage of the DC bus of the DRES interface.

The control strategy is based on a cascade control with an outer voltage control loop which provides de current reference to the inner current control loop defined in the previous controller. In this way, the energy of the UC is used to maintain the DC voltage in the high side of the DC/DC converter corresponding to the DC bus of the DC/DC converter. This control strategy is depicted in Fig. 10.

Fig. 10. Block diagram of the voltage controller for DC/DC converters.

#### 3. Control strategy for UC voltage of DRES interface.

The voltage of the UC must be maintained within its technical limits (90-150 V for the UC of the DRES interface) that avoid undervoltages or overvoltages that could damage the UC or a malfunction of the DRES interface. In this way, an energy source is required to absorb or inject the energy necessary to keep the UC within these limits. This energy source can be the low voltage network of the laboratories or the Grid Emulation. The UC connection to this source requires that both the DC / DC converter and the DC / AC converter be operational at the same time. The DC / DC converter in voltage control operation mode and the DC / AC converter in power control mode. An active power can be defined for the DC / AC converter in order to charge or discharge the UC. This power is computed from a proportional controller applied to the error of a UC voltage reference and the actual voltage of the UC. This controller is a proportional because the energy of the UC must have certain freedom to provide the AS corresponding to inertia and HFPS. The control strategy of the UC voltage is depicted in Fig. 11 representing the control strategy involved in each power converter.

Fig. 11. Block diagram of the UC voltage controller.

#### 4. Control strategy for PV emulator.

PV emulator is a commercial power converter accessible through a user interface where the modes of operation of this device can bed defined. These are DC current control or DC voltage control. In addition, the maximum allowed operating limits for the current and voltage provided by the PV emulator must be defined. If any of these limits are reached, the PV is able to automatically change its mode of operation so as not to exceed the limits imposed.

#### 5. Control strategy for Grid Emulation

Grid Emulation is also a power converter composed of a back-to-back topology with two VSCs sharing a common DC bus. One VSC is connected to the low voltage grid of the laboratory and it is in charge to control the voltage of the common DC bus of both VSCs. Second VSC is in charge to create an AC voltage at its terminal with a desired amplitude and frequency. An user interface is used to define the voltages at the terminal of the second VSC.

#### 6. Control of Zero current circulation

The connection of power electronics equipment with different control strategies, switching frequencies, PWM techniques etc ... can lead to a malfunction of the system if certain measures are not implemented. The most serious problem would be the zero current circulation if there is the possibility of forming a current loop between the connection of the equipment and the low voltage network of the laboratories [17]. To avoid this problem, the most feasible technique is to install a transformer with a delta connection that prevents zero current flow.

# 4.3.3 Monitoring aspects

The secondary controller of the DRES interface allows to monitor in real-time the voltage of the UC, the voltage of the DC bus, the rms AC current and voltage of the DC/AC converter and the DC current circulating into the UC. Moreover, an oscilloscope with four channels is used to measure and record four measurements. These can be selected from these group of signals: *abc* current injected to the PCC of the DC/AC converter, *abc* voltage of the AC/DC converter, DC current of the UC and DC voltage of the UC. Finally, the local controller of the Grid Emulation is also used to recorded currents, voltages and powers injected from the DC/AC converter to the Grid Emulation.

### 4.4 Data Management and Processing

Measurements of each test defined in section 4.1 are recorded in an oscilloscope in two ways: a csv file with the data of the 4 channels and an image of the oscilloscope screen. These data is extracted from the oscilloscope and recorded in a common cloud shared between TUDelft and Universidad de Sevilla. During and after each test, the signals monitored in the oscilloscope are analyzed to check if the tracking of references consigned to the controllers is being carried out properly.

#### 5 Results and Conclusions

The results obtained of the most important tests defined in section 4.1 are discussed below. Due to the large number of tests, devices and control strategies involved in these experiments, a table identifying each of these aspects will be used at the beginning of each test discussion.

### 5.1 Unitary Tests

# 1. AC/DC converter working in Grid-Feeding mode and connected to grid through a transformer

| DC/AC converter | DC/DC converter | Grid Emulation | PV Emulator |

|-----------------|-----------------|----------------|-------------|

| Х               |                 |                |             |

| DC/AC converter                   | DC/AC converter | DC/AC converter  | DC/DC           | DC/DC          |

|-----------------------------------|-----------------|------------------|-----------------|----------------|

| Grid-feeder cur-                  | Grid-feeder     | Grid-feeder as a | converter       | converter      |

| rent control id                   | power control P | STATCOM          | Current control | Voltage        |

| and <i>iq</i>                     | and Q           |                  | of the DC/DC    | control of the |

|                                   |                 |                  | converter       | DC/DC          |

|                                   |                 |                  |                 | converter      |

|                                   |                 | X                |                 |                |

| Control strategy                  | PV emulator     | PV emulator      | Grid Emulation  | Transformer    |

| for UC voltage of DRES interface. | Current source  | Voltage source   | Voltage source  |                |

|                                   |                 |                  |                 | X              |

|                                   |                 |                  |                 | ^              |

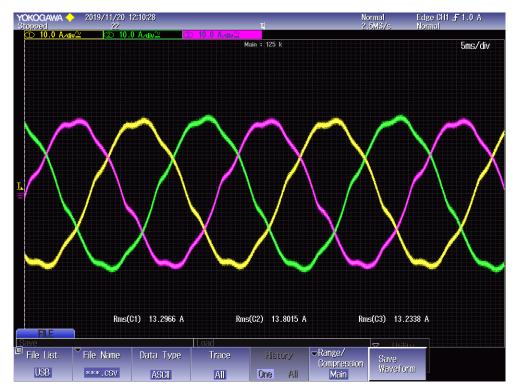

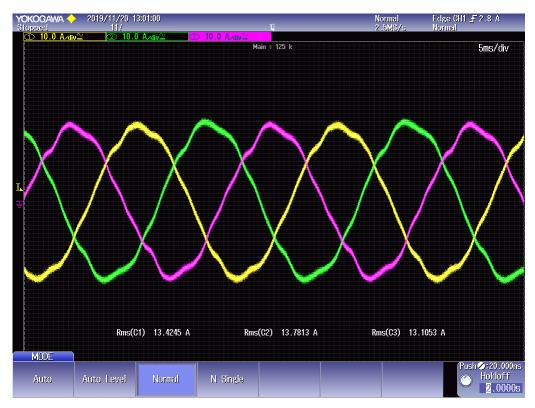

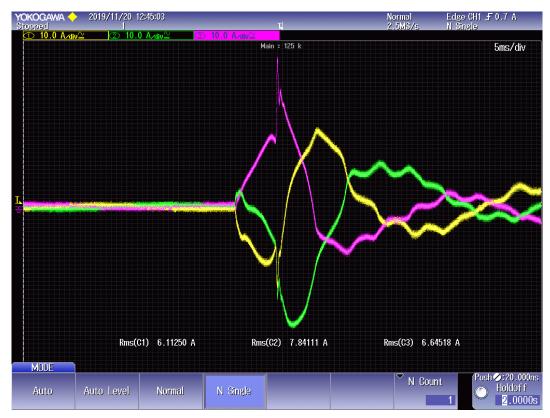

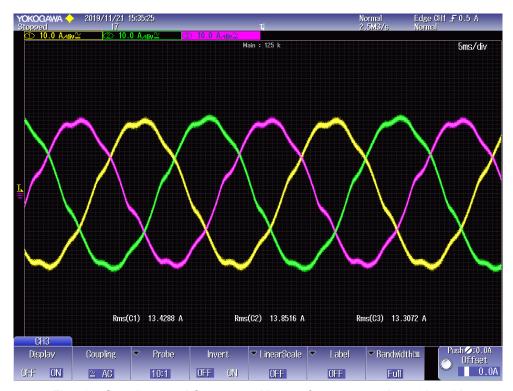

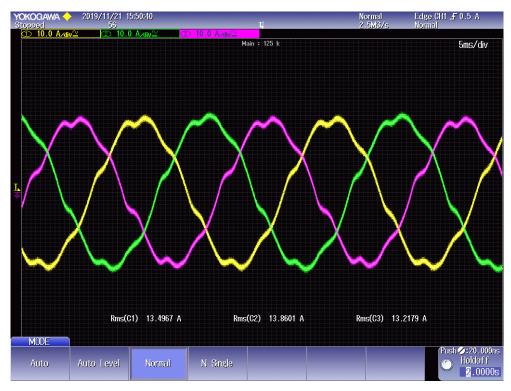

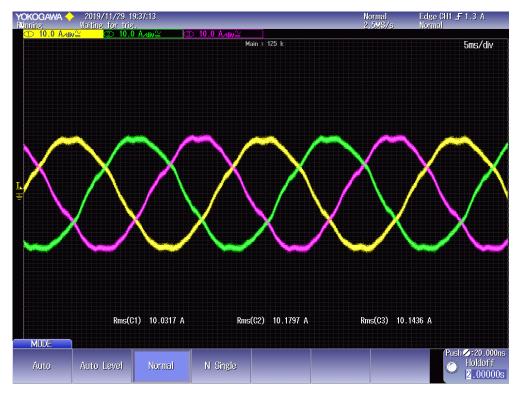

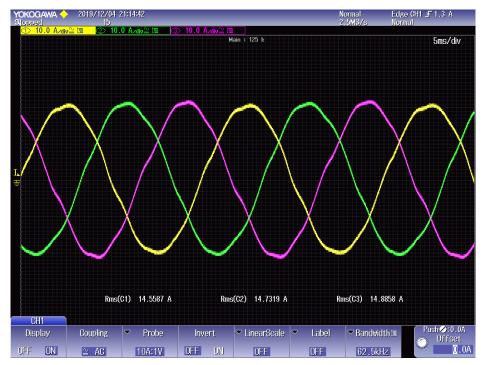

The DC/AC converter is in charge of controlling its DC bus and the current *id* injected into the PCC. A Dyn5 transformer with several tap ratios is connected among the DC/AC converter and the low voltage network. These tap ratios are: 240/400 V and 360/400 V. The AC side of the converter is connected to the low voltage side of the transformer. The setpoints of the DC/AC converter are 730 V for the DC voltage and a current *id* which is increased progressively until 20 A. The results for the different tap ratios are depicted from Fig. 12-Fig. 14 in steady- and transient-state. The steady-state represents the *abc* currents when the setpoint is defined in 20 A and the transient-state represents the initial *abc* currents the initial DC/AC converter interconnection to the low voltage laboratory grid.

The results in steady-state for the different tests shown that the current reference of 20 A is tracked. The current *id* must correspond to the peak of the currents in *abc* which are equal to 20 A. However, the waveform of the currents is quite distorted due to the low frequency harmonics of the laboratory network. This effect is increased because of the transformer. This is because the mag-

netic package of the transformer used is of low quality amplifying the low voltage harmonics. The transient connection shows a high current to control the DC bus until the controller acts and begins to gradually reduce the current until the reference is reached. The current id set at the time of connection is 0 A. Moreover, this high current at the time of interconnection is only limited by the inductive part of the DC / AC converter coupling filter. This has been greatly reduced in the DRES interface using an LCL filter so that the ability to inject reactive power through the AC / DC converter is as high as possible.

Fig. 12. Steady-state AC current with transformer tap ratio 240/400 V.

Fig. 13. Transient-state AC current with transformer tap ratio 240/400 V.

Fig. 14. Steady-state AC current with transformer tap ratio 360/400 V.

# 2. AC/DC converter working in Grid-Feeding mode and connected directly to grid

| DC/AC converter | DC/DC converter | Grid Emulation | PV Emulator |

|-----------------|-----------------|----------------|-------------|

| Х               |                 |                |             |

| DC/AC converter<br>Grid-feeder cur-<br>rent control id<br>and iq | DC/AC converter<br>Grid-feeder<br>power control P<br>and Q | DC/AC converter<br>Grid-feeder as a<br>STATCOM | DC/DC<br>converter<br>Current control<br>of the DC/DC<br>converter | DC/DC<br>converter<br>Voltage<br>control of the<br>DC/DC<br>converter |

|------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------|

|                                                                  |                                                            | X                                              |                                                                    |                                                                       |

| Control strategy for UC voltage of DRES interface.               | PV emulator<br>Current source                              | PV emulator<br>Voltage source                  | Grid Emulation<br>Voltage source                                   | Transformer                                                           |

|                                                                  |                                                            |                                                |                                                                    |                                                                       |

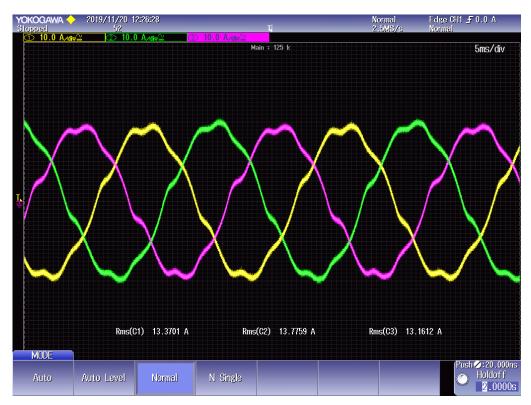

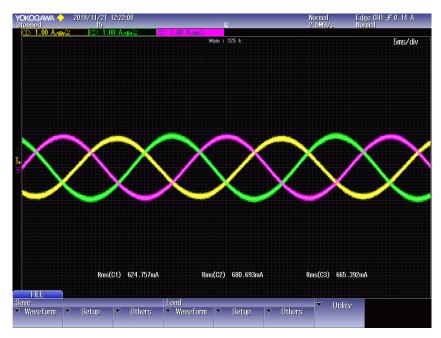

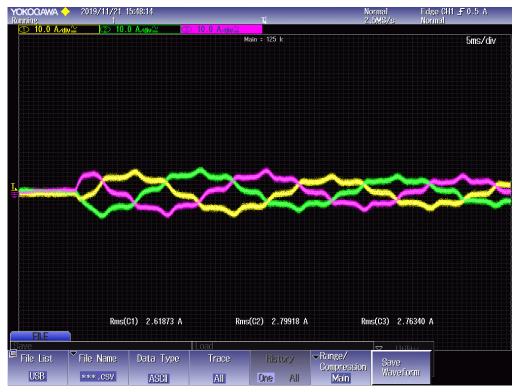

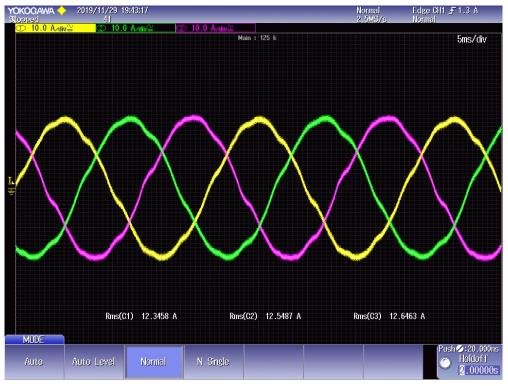

A transformerless connection is made the AC/DC converter and the low voltage laboratory network. The control strategy and setpoints are identical to the previous test. The results are depicted in Fig. 15-Fig. 16. The waveform is slightly improved compared to the case with interconnection transformer. However, the effect of low voltage harmonics is still present in the waveform of the currents.

Fig. 15. Steady-state AC current transformerless connection.

Fig. 16. Transient-state AC current transformerless connection.

### 3. Open Loop AC/DC converter. Voltage Controller DC/DC converter

| DC/AC converter | DC/DC converter | Grid Emulation | PV Emulator |

|-----------------|-----------------|----------------|-------------|

| X               | Х               |                |             |

| DC/AC converter<br>Grid-feeder cur-<br>rent control id<br>and iq | DC/AC converter Grid-feeder power control P and Q | DC/AC converter<br>Grid-feeder as a<br>STATCOM | DC/DC<br>converter<br>Current control<br>of the DC/DC<br>converter | DC/DC<br>converter<br>Voltage<br>control of the<br>DC/DC<br>converter |

|------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------|

| Control strategy for UC voltage of DRES interface.               | PV emulator<br>Current source                     | PV emulator<br>Voltage source                  | Grid Emulation<br>Voltage source                                   | Transformer                                                           |

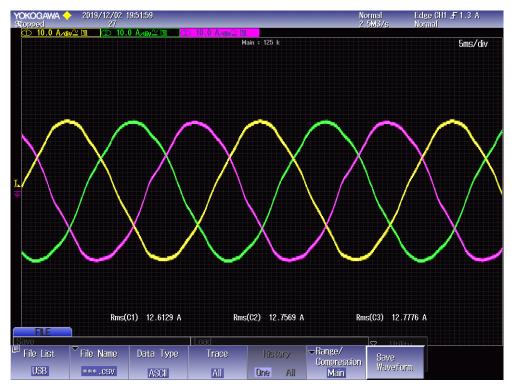

The DC / DC converter controls the DC bus voltage of the DRES interface using the power of the UC. The DC/AC converter is operated in open loop. This means that perfect sinusoidal control signals are provide by the user to the power converter. The AC output of the converter is connected to a resistive load. The energy supplied to the resistors is extracted from the energy of the UC.

Fig. 17 represents the *abc* currents of the AC/DC converter circulating toward the resistors. The setpoint defined for the DC bus is 730 V and the duty ratio defined for the open loop test is 0.9. This figure shows a perfect sinusoidal signals according to the reference defined in the open loop test. Moreover, this indicates that the DC voltage is constant and tracking the setpoint properly. A bad tracking of the DC voltage will cause oscillation in the waveform of the *abc* currents.

Fig. 17. Steady-state abc currents injected from the AC/DC converter to the resistors in open loop test

# 4. Grid-Feeding connected to grid through a transformer AC/DC converter. Voltage Controller DC/DC converter.

| DC/AC converter | DC/DC converter | Grid Emulation | PV Emulator |

|-----------------|-----------------|----------------|-------------|

| Х               | X               |                |             |

| DC/AC converter<br>Grid-feeder cur-<br>rent control id<br>and iq | DC/AC converter<br>Grid-feeder<br>power control P<br>and Q | DC/AC converter<br>Grid-feeder as a<br>STATCOM | DC/DC<br>converter<br>Current control<br>of the DC/DC<br>converter | DC/DC<br>converter<br>Voltage<br>control of the<br>DC/DC<br>converter |

|------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------|

| X                                                                |                                                            |                                                |                                                                    | X                                                                     |

| Control strategy for UC voltage of DRES interface.               | PV emulator<br>Current source                              | PV emulator<br>Voltage source                  | Grid Emulation<br>Voltage source                                   | Transformer                                                           |

|                                                                  |                                                            |                                                |                                                                    | Х                                                                     |

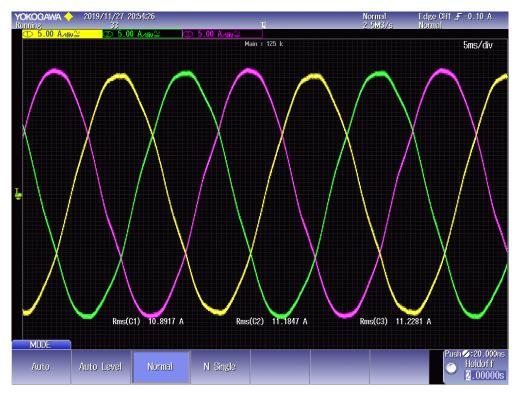

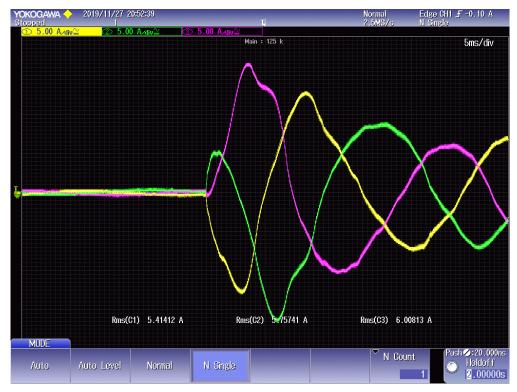

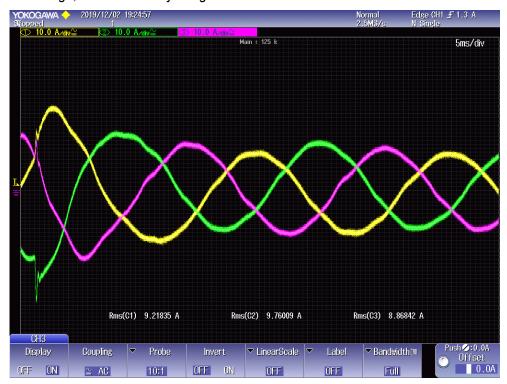

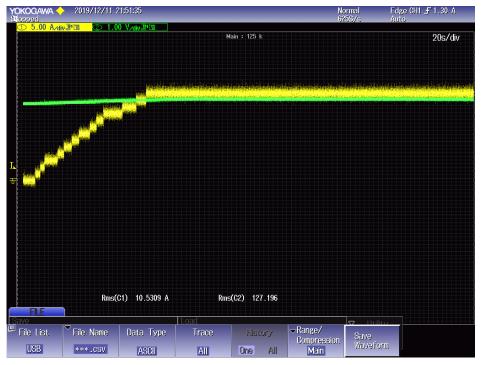

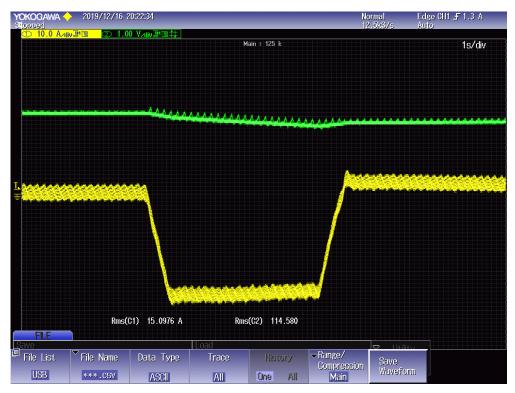

The DC/DC converter is in charge to control the DC bus of the DRES interface using the energy of the UC. While the AC/DC converter controls the current *id* and *iq* injected to the grid with an interconnection transformer. The active power (*iq*) injected/absorbed to/from the grid is obtained from the UC.